# Role of Computers in Engineering

Izad Khormaee Engineering Department Clark College 1/22/2005

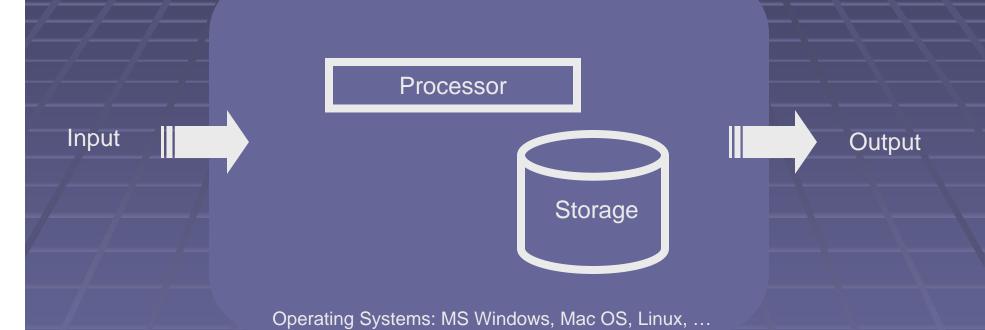

# What is a computer?

# Where are computers used?

## Computer Usages

- Everyday Living

- Office Productivity

- Engineering Specialized Tools

- Engineering Applications Software

### Computers for Everyday Life

- Cars

- Cell Phones

- Home Appliances

- Watches

- Games

- Buildings

- Vending Machines

- /...

#### Office Productivity

- Word Processing (MS Word)

- Spread Sheet (MS Excel)

- Presentation (MS PowerPoint)

- Database (MS Access)

- Project Planning (MS Project)

■ ...

# Engineering Specialized Tools

- Calculators (HP 45 and TI 89)

- Surveyor Tool

- Oscilloscope

- Strain Gauge

- Laser Leveler

- Pneumatic Machines

- **-** ...

#### Engineering Applications Software Iteration Speed Cost Idea for New Product or Service Design **Test** Computer Aided Design (CAD) Prototype Computer Aided Test (CAT) Manufacturing Computer Aided Manufacturing (CAM) Page 8

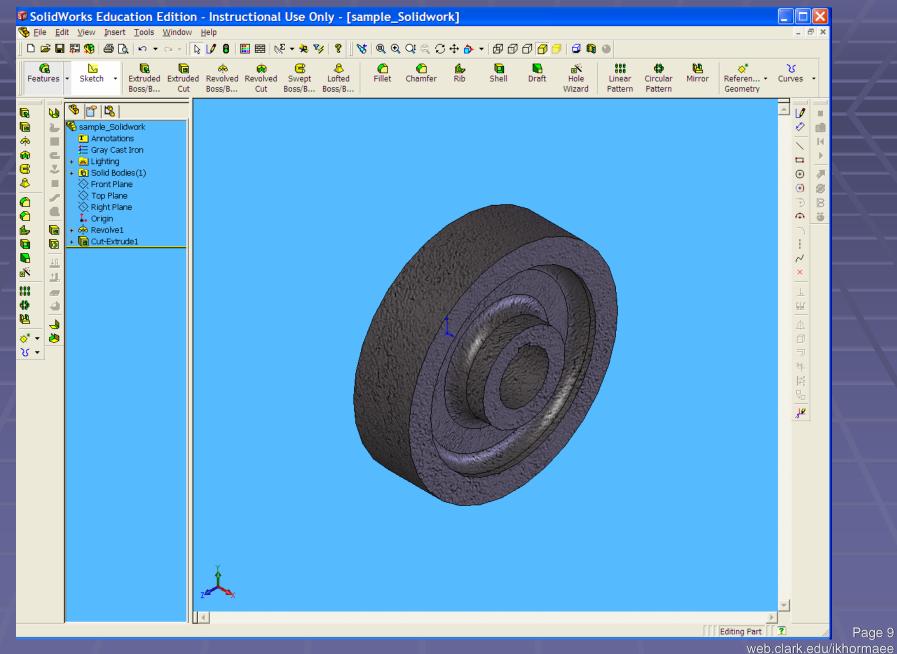

#### SolidWorks, Parametric Solid Modeler

"Changing parameter values will change the drawing"

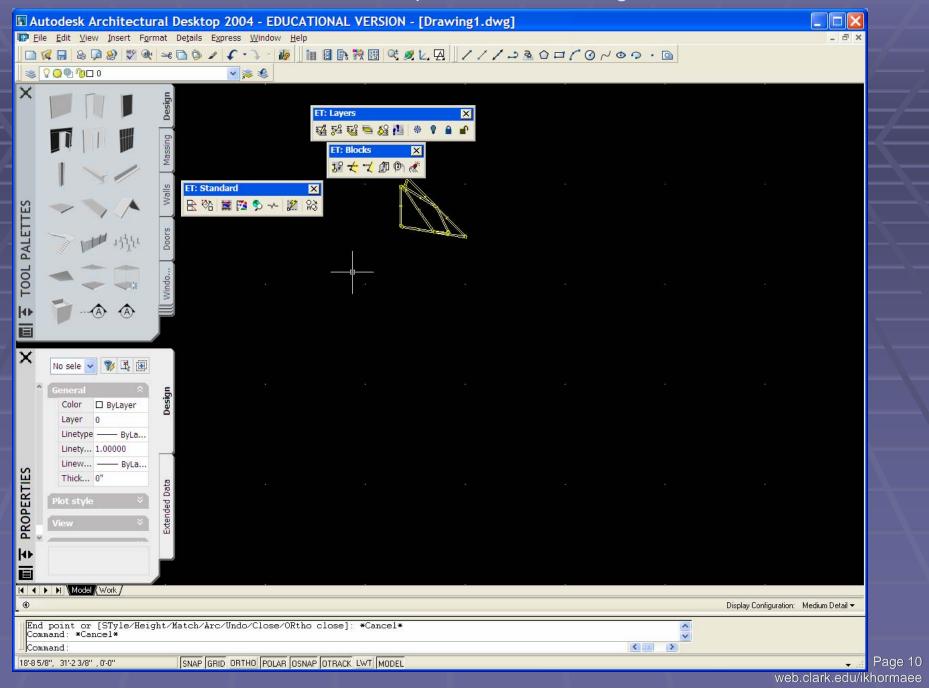

#### AutoCAD, Computer Aided Drafting

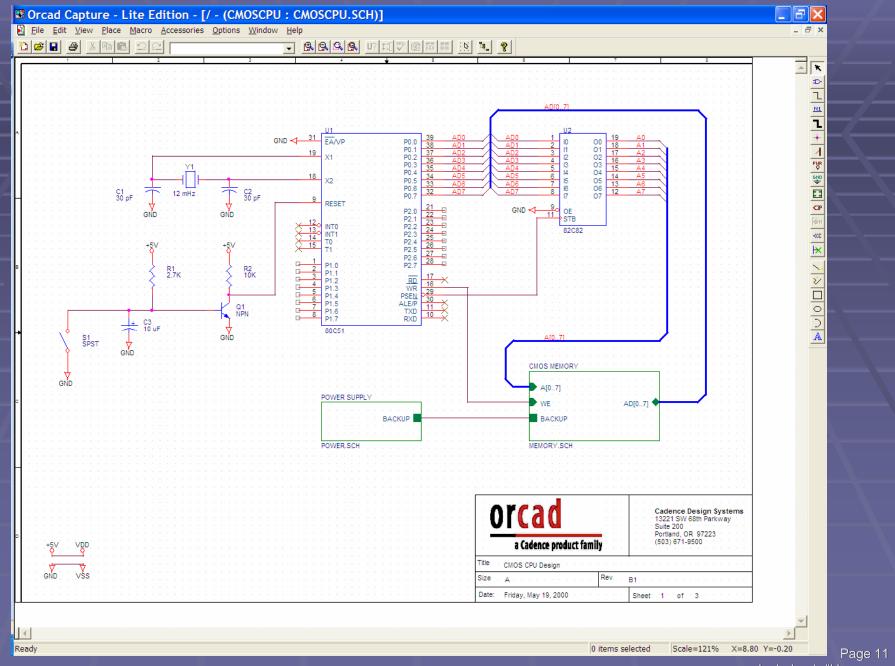

#### PSpice, Electronic and Digital Design/Testing Environment

#### MatLab, Engineering Programming Environment *MATLAB MATLAB* <u>File Edit View Web Window Help</u> Current Directory: C:WATLAB6p5\work C:\MATLAB6p5\toolbox\matlab\demos\splashdemo.m Name File Edit View Text Debug Breakpoints Web Window Help che" for more info function splashdemo Figure No. 1 % SPLASHDEMO Plot the L-shaped membrane with semitranspare File Edit View Insert Tools Window Help % Copyright 1984-2002 The MathWorks, Inc. □ ☎ 日 番 ト A オ / 9 9 つ % \$Revision: 1.3 \$ \$Date: 2002/04/08 20:04:53 \$ L = 40\*membrane(1,25);% Generate a circular alphadata for the mesh. 10 [j,i] = meshgrid(l:size(L,l)); 11 alphadata = $sqrt((i-4).^2 + .8*(j+4).^2);$ 12 13 % This alphamap causes there to be a thin band that 14 % is semi-transparent, as opposed to the entire surface 15 fig = figure; 16 set(fig, 'Color', 'white',... 17 'AlphaMap',... 18 [ zeros(1,40), ... 19 linspace(0,.5,15), linspace(.5,1,8), ... 20 ones(1,30)]); 21 22 axes('CameraPosition', [-193.4013 -265.1546 220.4819],... 23 'CameraTarget',[26 26 10], ... 24 'CameraUpVector',[0 0 1], ... 25 'CameraViewAngle',9.5, ... 26 'DataAspectRatio', [1 1 .9],... 27 'Position',[0 0 1 1], ... Workspace 28 'Visible', 'off', ... 29 'XLim',[1 51], ... 30 'YLim',[1 51], ... x=a\b 31 'ZLim',[-13 40]); =-8\*(-16.2) -5\*(-11. 32 -8\*(-16.2) -5\*(-11.5 33 % This surface represents a white opaque surface with edge a = [28,-20, -8; -20 34 sl = surface(L, ... x=a\b 35 'FaceColor', 'white', ... %-- 1/22/05 11:57 AM 36 'FaceLighting', 'none', ... cls 37 'Clipping','off',... clr 38 'EdgeColor',[.8 .8 .8]); clear % This represends the colored surface. cls clear splashdemo Ln 37 %-- 1/22/05 12:24 PI ♠ Start Page 12

web.clark.edu/ikhormaee

#### VHDL, Hardware Description Language ➡Xilinx - Project Navigator - C:\Data\gold code vhd 217\gold code vhd 217.npl - [vhd subb] File Edit View Project Source Process Window Help **→** 36 36 38 9 Pa 🖺 🖭 🖂 🙀 library ieee; Sources in Project: 2 use ieee.std logic 1164.all; ⊡... 🗖 Untitled readme 4⇔ entity LFSR\_B is xc2s15-6cs144 5 generic (cycleB0 : integer := 26; gold\_code-gold\_code\_arch (vhd\_top.vhd) cycleB20 : integer := 21; testbench-behavior (gold\_code\_tb.vhd) width :integer := 1); Ifsr\_a-Ifsr\_a\_arch (vhd\_suba.vhd) port ( Clk :in std logic; | Ifsr\_b-Ifsr\_b\_arch (vhd\_subb.vhd) Enable : in std logic; Fill En : in std\_logic; New\_Fill : in std\_logic\_vector(width -1 downto 0); DelayB0 :out std logic vector(width - 1 downto 0)); 14 attribute clock node :boolean; 15 attribute clock node of Clk : signal is TRUE; 17 end LFSR B; 18 19 architecture LFSR B ARCH of LFSR B is 20 signal Data In B: STD LOGIC VECTOR (width -1 downto 0); signal DelayB20 : STD LOGIC VECTOR (width -1 downto 0); signal DelayB0\_int : STD\_LOGIC\_VECTOR(width -1 downto 0); Module View Snapshot View Library View type my\_type is array (0 to cycleB0 -1) of std\_logic\_vector(width -1 downto 0); signal int sigB0 :my type; 26 27 28 29 type my\_type2 is array (0 to cycleB20 -1) of std\_logic\_vector(width -1 downto 0); signal int sigB20 :my type2; Processes for Source: "gold\_code-gold\_code\_arch" Add Existing Source Create New Source begin 30 Design Entry Utilities main :process (Clk) Create Schematic Symbol View Command Line Log File if Clk'event and Clk = '1' then View VHDL Instantiation Template 34 if (Enable = '1') then User Constraints ā 35 int\_sigB0 <= Data\_In\_B & int\_sigB0(0 to cycleB0 - 2);</pre> Synthesize - XST 36 int sigB20 <= Data In B & int sigB20(0 to cycleB20 - 2); ⊕ G Implement Design 37 end if; Generate Programming File 38 if (Fill En = '0') then Data In B <= DelayB20 xor DelayB0 int; 40 Data In B <= New Fill; 42 end if; 43 end if; end process main; 45 46 delayB0 int <= int sigB0(cycleB0 -1); delau820 /= int eig820/gugle820 - 1). vhd\_subb Process View Warning: This process is used to display the running command log file that records some application command lines. If you haven't run any process yet, this file couldn't be generated. Please run some processes to create the running command log file Console Find in Files Warnings Errors Page 13 For Help, press F1 Ln 4 Col 1 web.clark.edu/ikhormaee

# Questions / Comments

Almost Done!